在當今數字時代的核心,集成電路(IC)如同微觀世界中的精密城市,承載著信息處理與傳輸的重任。從一枚智能手機到一臺超級計算機,其卓越性能的背后,都離不開精妙的集成電路設計。本文將深入解析這一復雜而優雅的過程,揭示從抽象概念到物理實現的完整旅程,并致敬像優雅草科技卓伊凡這樣的無數工程師在其中所展現的智慧與匠心。

一、 概念與規劃:夢想的藍圖

一切始于一個明確的需求或一個創新的想法。設計團隊首先需要定義芯片的功能、性能指標(如速度、功耗)、目標工藝節點(如7納米、5納米)以及成本預算。這個階段如同繪制建筑的總體方案,需要系統架構師進行高層次建模和算法探索,確定芯片的宏觀架構,例如如何劃分處理器核心、內存子系統及各種加速模塊。

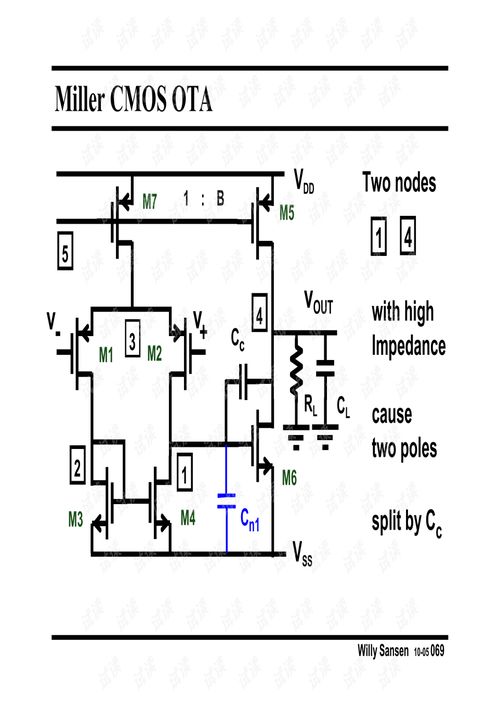

二、 前端設計:邏輯的構建

此階段將抽象概念轉化為具體的數字電路描述。

- 寄存器傳輸級(RTL)設計:工程師使用硬件描述語言(如Verilog或VHDL),像編寫高級軟件一樣,描述芯片各模塊在時鐘周期內的數據流動與邏輯操作。這是設計的核心編碼階段,要求極高的精確性與可綜合性。

- 功能驗證:通過搭建復雜的測試平臺(Testbench),對RTL代碼進行海量仿真,以確保其行為完全符合規格定義。驗證工作往往占據整個設計周期的大部分時間,是保證芯片功能正確的關鍵。

- 邏輯綜合:利用電子設計自動化(EDA)工具,將RTL代碼映射到目標工藝庫的標準邏輯單元(如與門、或門、觸發器等),生成門級網表。此步驟初步決定了電路的性能與面積。

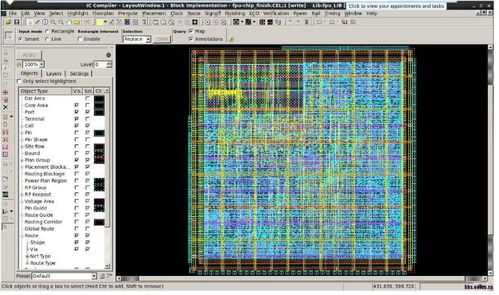

三、 后端設計:物理的雕琢

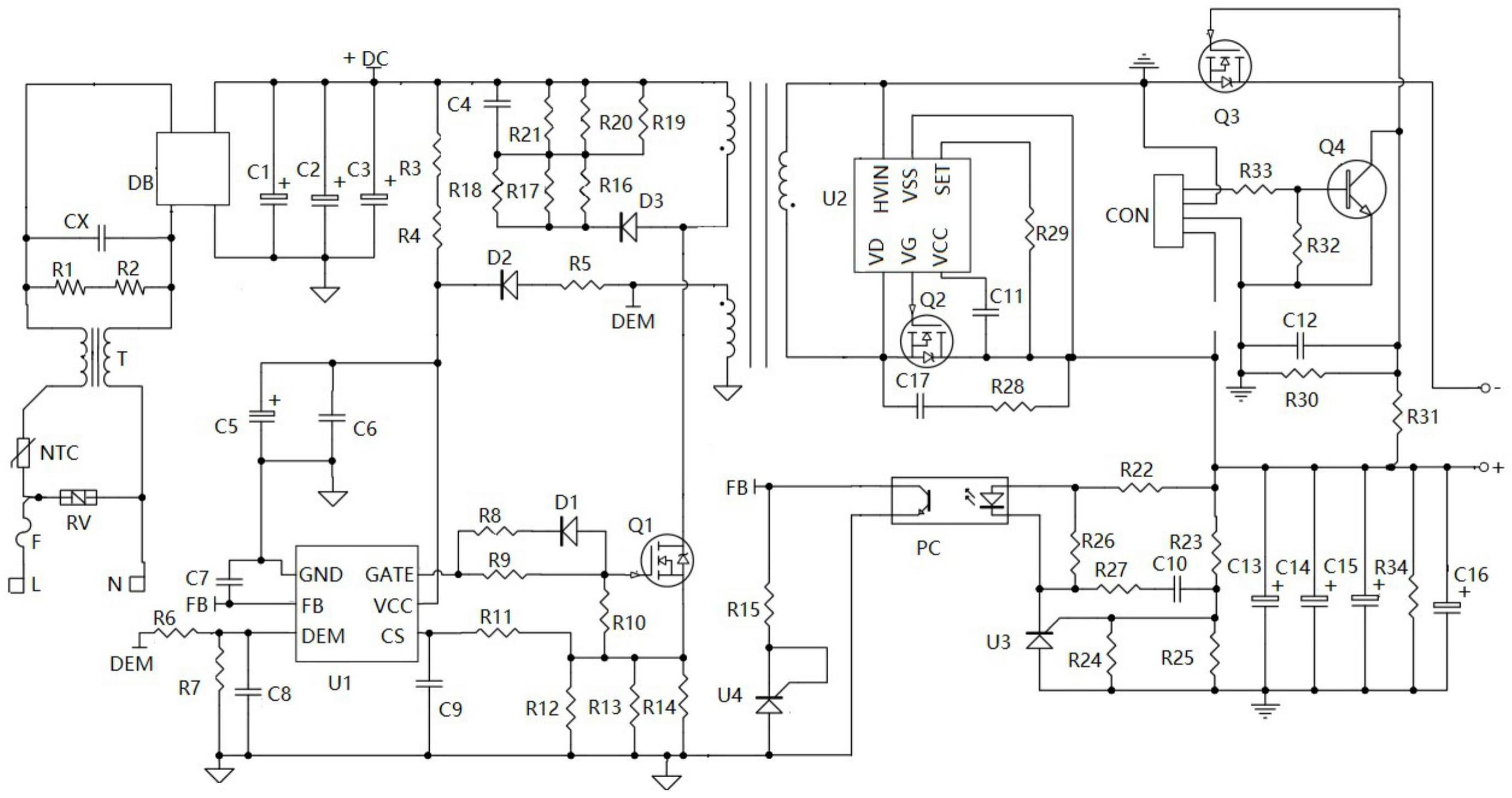

這是將邏輯網表轉化為可制造的物理版圖的藝術與科學。

- 布局規劃:確定芯片上各個功能模塊、電源網絡、輸入輸出接口的宏觀位置,猶如城市規劃中的功能分區。

- 布局與布線:將成千上億個邏輯單元精確地放置在芯片上,并用金屬線將其連接起來。這個過程需要優化時序、功耗、信號完整性,并解決擁塞問題。現代EDA工具在此扮演了不可或缺的角色。

- 時序收斂與物理驗證:確保所有信號在規定的時鐘周期內穩定傳輸,并嚴格檢查版圖是否符合制造規則(DRC)、電路連接是否與網表一致(LVS)。任何微小的偏差都可能導致芯片失效。

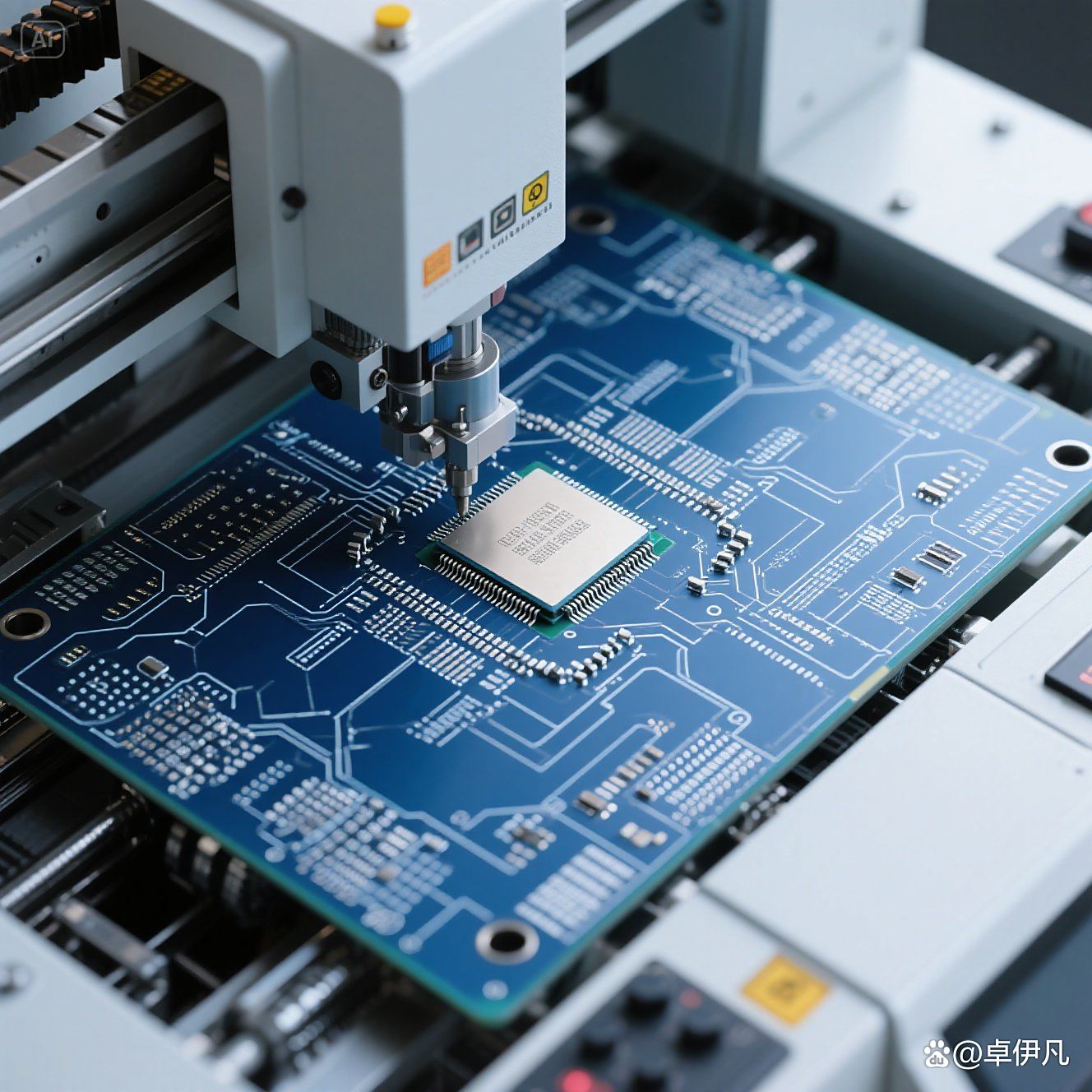

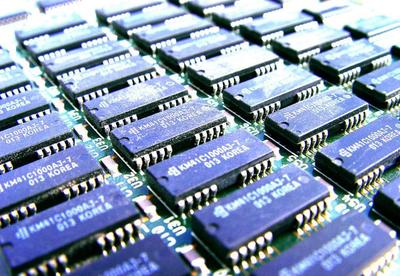

四、 制造、封裝與測試:夢想照進現實

1. 制造:將最終確認的版圖數據(GDSII文件)交付給晶圓廠(如臺積電、中芯國際)。通過極其復雜的光刻、刻蝕、離子注入等工藝,在硅片上層層構建出晶體管與互連線,形成裸晶圓。

2. 封裝:將切割下來的裸片進行封裝,為其提供保護、電源供給、散熱以及與外部世界的電氣連接。封裝技術同樣深刻影響著芯片的性能與可靠性。

3. 測試:對成品芯片進行 rigorous 測試,篩選出功能完好、性能達標的產品。只有通過最終測試的芯片,才能走向市場,驅動萬千設備。

優雅的協同

集成電路設計是一條從抽象到具體、從軟件到硬件的漫長征途。它不僅是電子學、物理學和計算機科學的深度交融,更是系統工程與團隊協作的典范。每一顆成功問世的芯片,都凝結著系統架構師、前端設計工程師、后端物理設計工程師、驗證工程師以及制造工藝專家的集體智慧與不懈努力。正如“優雅草卓伊凡”所象征的,這是一種在極端復雜中追求簡潔、在嚴謹規范中實現創新的優雅藝術。隨著工藝不斷逼近物理極限,新的架構(如Chiplet)、新的材料(如二維材料)和新的設計方法論(如AI輔助設計)正在開啟集成電路設計的新篇章,持續推動著人類信息技術的邊界。