模擬集成電路(Analog Integrated Circuit, AIC)設計是電子工程領域的核心技術之一,它涉及將連續的模擬信號(如聲音、溫度、壓力等)在微小的硅芯片上進行處理、放大和轉換。與數字集成電路處理離散的0和1信號不同,模擬電路處理的是連續變化的電壓或電流,這對設計的精度、噪聲抑制和功耗控制提出了極高要求。本文旨在為初學者和從業者提供一個全面的緒論性指導,涵蓋模擬集成電路設計的基本概念、關鍵流程、核心挑戰以及學習資源推薦。

一、模擬集成電路設計的基本概念

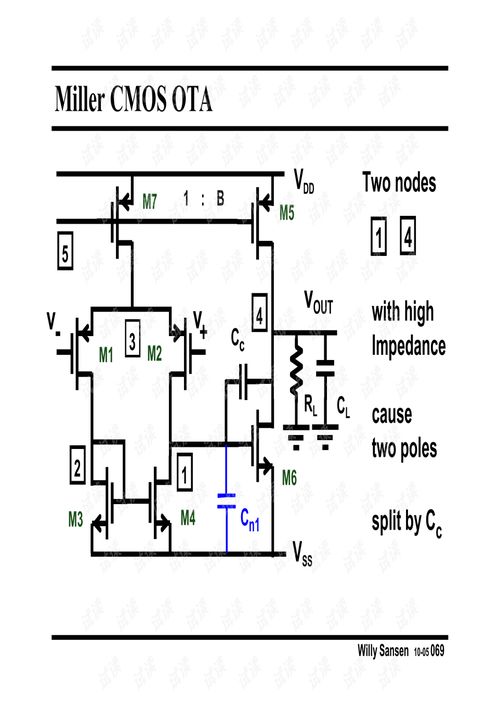

模擬集成電路的核心任務是在硅片上實現特定的模擬功能模塊,如運算放大器、濾波器、數據轉換器(ADC/DAC)、電源管理芯片等。設計過程始于系統級規劃,明確芯片的性能指標(如增益、帶寬、功耗、線性度),然后通過晶體管級電路設計、仿真驗證、版圖繪制和流片測試等多個階段實現。設計師需要深刻理解半導體物理、器件模型(如MOSFET、BJT)、電路理論以及工藝制程的相互作用。

二、設計流程與工具

典型的模擬集成電路設計流程包括:

- 規格定義:根據應用需求確定芯片的功能和性能參數。

- 電路設計:使用器件模型搭建電路圖,常用工具包括Cadence Virtuoso、Synopsys HSPICE等。

- 仿真驗證:通過直流、交流、瞬態和噪聲仿真來評估電路性能,確保滿足規格要求。

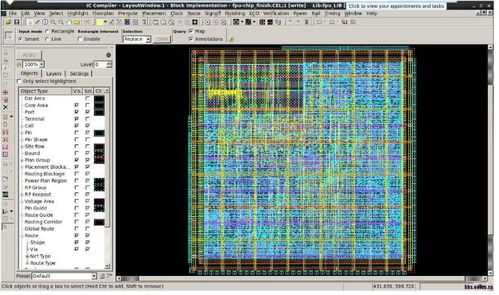

- 版圖設計:將電路圖轉換為物理布局,考慮匹配性、噪聲隔離和寄生效應,工具如Cadence Virtuoso Layout。

- 后仿真:提取版圖寄生參數后重新仿真,驗證實際性能。

- 流片與測試:提交設計到晶圓廠制造,并對芯片進行實測驗證。

三、核心挑戰與趨勢

模擬集成電路設計面臨諸多挑戰:工藝變異導致的性能波動、電源電壓下降帶來的動態范圍限制、高頻應用下的噪聲和串擾問題等。隨著工藝節點不斷縮小,模擬電路設計更需兼顧與數字電路的混合集成(如SoC設計)。當前趨勢包括低功耗設計、高精度數據轉換、射頻集成以及人工智能輔助設計工具的應用。設計師必須持續學習新技術,例如FinFET器件模型和先進封裝技術。

四、學習資源推薦

對于初學者,專業指導文檔和課程至關重要。CSDN等平臺提供了豐富的資源下載,包括:

- 《模擬CMOS集成電路設計》經典教材的筆記和習題解答。

- 行業大牛的設計實例和版圖技巧分享。

- 仿真工具使用教程和腳本模板。

- 最新會議論文和工藝文檔的解讀。

建議結合理論教材(如Razavi或Gray的著作)與動手實踐,通過開源工具或教育版軟件進行項目練習,逐步掌握從概念到流片的完整技能。

###

模擬集成電路設計是一門融合藝術與科學的學科,要求設計師兼具創新思維和嚴謹態度。通過系統學習基礎理論、掌握設計工具并關注行業動態,工程師可以在這個關鍵領域發揮重要作用,推動通信、醫療、汽車等行業的科技進步。無論你是學生還是從業者,持續探索和實踐將是通往成功的必由之路。