電源集成電路(Power IC)及電源集成模塊是現(xiàn)代電子設(shè)備能量管理的核心,其設(shè)計與制造水平直接決定了電子系統(tǒng)的效率、穩(wěn)定性與小型化程度。本文將深入探討其設(shè)計流程、關(guān)鍵技術(shù)及制造工藝。

一、設(shè)計理念與流程

電源IC設(shè)計始于明確的規(guī)格定義:包括輸入/輸出電壓范圍、輸出電流、效率目標(biāo)、紋波要求及保護功能(如過壓、過流、過熱保護)。設(shè)計采用自上而下的方法:

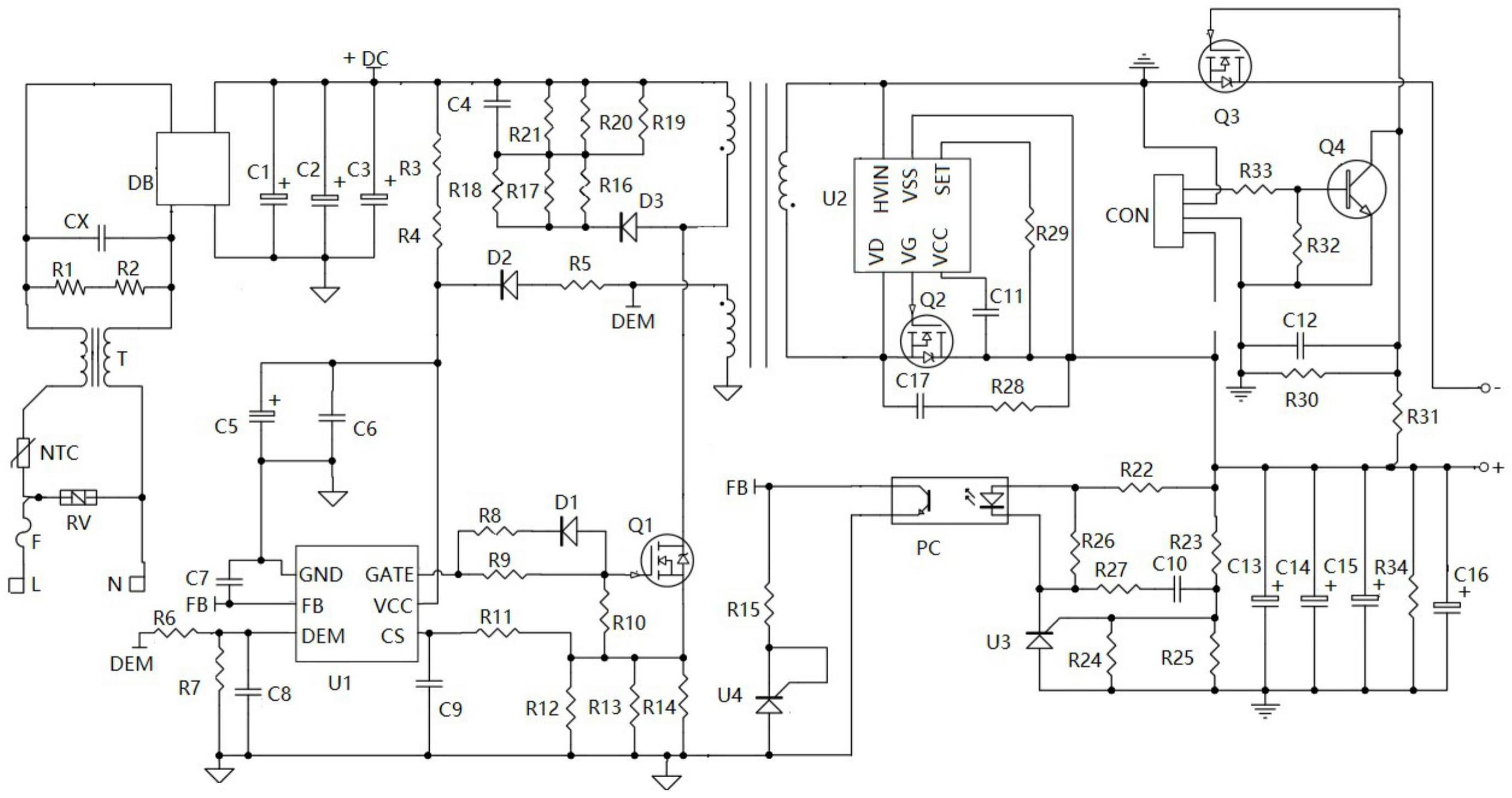

- 架構(gòu)選擇:根據(jù)應(yīng)用場景(如線性穩(wěn)壓器LDO、開關(guān)穩(wěn)壓器DC-DC、AC-DC控制器)確定拓?fù)浣Y(jié)構(gòu)(Buck、Boost、Buck-Boost等)。

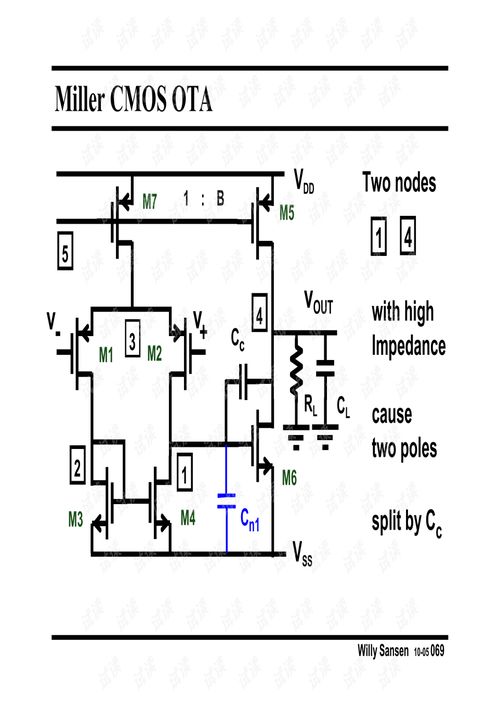

- 電路設(shè)計:使用EDA工具進(jìn)行晶體管級設(shè)計,重點優(yōu)化功率管、誤差放大器、振蕩器、驅(qū)動電路及反饋網(wǎng)絡(luò)。

- 仿真驗證:通過SPICE等工具進(jìn)行功能、性能及可靠性仿真,確保在各種工況下滿足指標(biāo)。

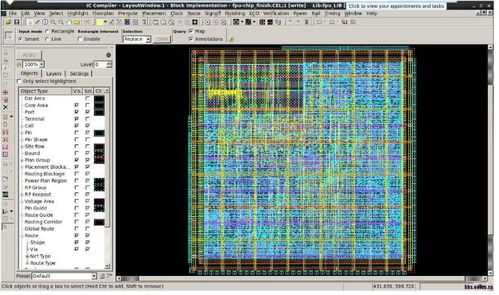

- 版圖設(shè)計:考慮高電流路徑、熱分布、電磁兼容性及工藝規(guī)則,進(jìn)行精密布局布線。

二、核心技術(shù)要點

- 功率器件集成:采用DMOS、LDMOS等工藝集成高壓大電流功率MOSFET,降低導(dǎo)通損耗。

- 控制算法:數(shù)字控制技術(shù)(如數(shù)字PID)與模擬控制結(jié)合,實現(xiàn)快速動態(tài)響應(yīng)與高精度調(diào)節(jié)。

- 熱管理設(shè)計:通過襯底材料選擇、散熱通孔及布局優(yōu)化,確保芯片結(jié)溫在安全范圍內(nèi)。

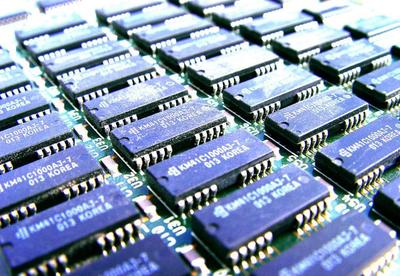

- 封裝集成:電源模塊將IC、電感、電容等無源元件集成于同一封裝內(nèi),采用系統(tǒng)級封裝(SiP)或嵌入式基板技術(shù),減少寄生參數(shù),提高功率密度。

三、制造與工藝挑戰(zhàn)

制造過程基于硅基或?qū)捊麕О雽?dǎo)體(如GaN、SiC)工藝。關(guān)鍵工藝包括:

- 特種工藝模塊:如BCD(Bipolar-CMOS-DMOS)工藝,能在同一芯片上集成高精度模擬電路、數(shù)字邏輯及功率器件。

- 三維集成:通過TSV(硅通孔)等技術(shù)實現(xiàn)多層堆疊,縮短互連長度,提升性能。

- 可靠性考量:需進(jìn)行嚴(yán)格的HTOL(高溫工作壽命)、ESD(靜電放電)等測試,確保產(chǎn)品在惡劣環(huán)境下穩(wěn)定工作。

四、未來發(fā)展趨勢

隨著物聯(lián)網(wǎng)、新能源汽車及人工智能設(shè)備對高效、小型化電源的需求增長,電源IC及模塊正朝著更高頻率(MHz以上)、更高效率(>95%)、更智能(自適應(yīng)調(diào)壓、故障預(yù)測)及更高集成度方向發(fā)展。寬禁帶半導(dǎo)體與先進(jìn)封裝技術(shù)的融合,將為下一代電源解決方案開辟更廣闊的空間。

電源集成電路及模塊的制作是一個多學(xué)科交叉的復(fù)雜工程,需要設(shè)計者在電路理論、半導(dǎo)體工藝、熱力學(xué)及封裝技術(shù)等領(lǐng)域具備深厚積累,方能打造出高效可靠的能源“心臟”。